-리눅스의 명령어를 사용 할 수 있다.

cd / = 루트경로로 이동

-> c와 d가 각각 c드라이브 d드라이브

------

1번 그림에서 압축푼 장소에서 CMD를 연다.

1. make

2. arm-elf-gcc

---- 데이터시트 ----

ARM은 보통 기본메모리가 4G이다.

데이터 시트의 20p

- 색이 칠해진 곳은 사용하지 않는 메모리.

주소공간이 크고 아트메가보다 많은 기능들을 내장하고있고 레지스터가 많다.

메모리가 4G인데 500M밖에 안씀

-메모리 순서-

내부 메모리(메모리 영역)

안쓰는 메모리

장치 메모리(CPU 영역)

-

장치에 관련된 레지스터들이 존재한다, 여기를 건드려야함. (128KB)

- 내부메모리는 256M를 사용하는데 확대모습을 보면 3M만 사용하고 색칠된 부분의

- 253M는 사용하지 않는다.

- Flash before Remap , SRAM after Remap이라고 적혀있는 구간은

- Remap을 하기전에는 Flash지만 Remap을 한 후에는 SRAM이다.

-

SRAM메모리가 위의 영역에 맵핑 되어 있다 라고 한다.맨 처음 부팅할때는 Flash메모리가 맨위에 올려져있다가 Remap을 하면 SRAM이맨위로 옮겨진 것 처럼 보인다. (제일 위에있는 구역(1M)는 사실 존재하지 않는다.)(실체는 밑의 flash와 sram이다.)

-

- SRAM이 1M로 되어있는데 데이터시트를 보면 실제 용량이 64KB이다.(1M중 64K사용)

-색칠된 부분은 안쓰는 메모리

SYSC를 확대한 모습

-아트메가는 하바드 구조인데 ARM은 폰 노이만 구조이다.

-아트메가는 flash가 떨어져있는데 ARM은 붙어있다.

---------------------------------------------------------------------------------------------------------------------------

-데이터 시트 -

27. Parallel Input/Output Controller (PIO)

PIO - Parallel Input/Output Controller (입/출력)

0부터 31까지 32비트의 크기를 가진 다리를 입출력 (회로를 인풋, 아웃풋)

PIO레지스터의 주소와 기준점 -

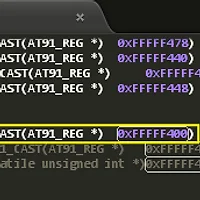

offset - 기준점 ( 어드레스가 아님 )으로부터 얼마나 떨어져있는지를 나타냄, 기준점은 0xFFFFF400

PIO Controller PIO Enable Register

활성화 레지스터

0을넣으면 아무런 영향 X

1은 활성화

PIO Controller PIO Disable Register

비활성화 레지스터

0을 넣으면 아무 영향 X

1은 비활성화

아트메가는 활성화 비활성화가 하나로 붙어있지만 ARM은 두개로 따로 분리되어있다.

0xFFFF F400

Read-only

읽기전용

쓰면 에러 X 아무런 효과가 없을 뿐

1이 들어가있으면 엑티브 상태

0은 비활성화

PIO Controller Output Status Register

출력이 활성화 되어있는지 확인 할 수 있음

PIO Controller Clear Output Data Register

0을 내보냄

PORT레지스터와 같다.

ex) PORTA = 0x01;

-나머지 8개에 H를 넣어도 L로 바뀌는 단점이 있다.

그래서 PORTA = PORTA | 0 >1 을 했는데 ARM은 그 단점을 극복함.

ARM은

PIO_SODR = 0x01;하면자신만 L되고 다른건 효과없음.

ATmega보다 훨씬 효율적.

---------------------------------------------------------------------------------------------------------------------------

---------------------------------------------------------------------------------------------------------------------------

어셈블리의 종류는 여러가지가 있는데 이(cstartup.S) 어셈블리코드는 C코드와 유사하다.

|

#include "project.h" /* 어셈블리인데 C코드와 유사함 */ #define TOP_OF_MEMORY (AT91C_ISRAM + AT91C_ISRAM_SIZE) #define ABT_STACK_SIZE 8*3*4 #define IRQ_STACK_SIZE 8*3*4 #define ARM_MODE_ABT 0x17 #define ARM_MODE_FIQ 0x11 #define ARM_MODE_IRQ 0x12 #define ARM_MODE_SVC 0x13 #define I_BIT 0x80 #define F_BIT 0x40 .globl reset_handler /* 어셈블리 스타일로 함수선언을 한 것 함수 이름이 reset_handler */

.align 4 .section .vectors /* section은 나누는 것을 의미 .vectors 변수 영역이다. */

.arm /* arm 소스라는 것을 의미하는 것 */ /* 앞에 .이 붙은것을 지시자라 부른다. (다이렉터, 디렉터)

이게 무엇이다~ 라는 것을 설명하는 영역 */

_exception_vectors: /* 위치를 나타내는 것 (라벨) */

/* 지금까지 어셈블리소스는 하나도 나오지 않았다. 지금까지는 컴파일러에게 설명하는 구간 */

reset_vector: /* 라벨 0 번지를 가리킴 */ ldr pc, =reset_handler /* 여기부터 어셈블리 코드가 시작. 0번지를 가리킴 */ /* ldr은 ld = lode r은 레지스터 즉 레지스터에 값을 집어넣어라 (대입) */

/* pc는 카운터 레지스터이다.(프로그램 카운터) = 실행을 해야하는 곳에 주소를 넣는 것

* 즉 이말은 실행을 하고 있다는 뜻 */

/* 어셈블리 문법이 보통 어떤 명령어 거기에 따른 인자들이 하나도 없는 경우도 있고 , 1, 2, 3, 4개 까지 있다. 앞의 인자에 따라 뒤가 정해진다. */

/* add A, B라면 A와 B를 더해서 더한값을 A에 넣는다. 어셈블리는 한줄이 명령어 한개이다. (C는 한줄일수도 있고......)*/

/* 0번지의 명령을 읽도록 회로적으로 만들어 놓음 0번지로 갔더니 reset_handler를 수행 하라고 함, reset_handler를 찾아 갔더니

* _low_level_init를 수행하라고 하고있다. r2, =_lp_ll_init를 수행함...-

* ldmia r2, {r0, r1} 부터 수행하고있음. */

undef_vector: b undef_vector swi_vector: b swi_vector pabt_vector: b pabt_vector dabt_vector: b dabt_vector rsvd_vector: b rsvd_vector irq_vector: b irq_handler fiq_vector: fiq_handler:

b fiq_handler irq_handler:

sub lr, lr, #4

stmfd sp!, {lr} mrs r14, SPSR

stmfd sp!, {r0,r14} ldr r14, =AT91C_BASE_AIC

ldr r0 , [r14, #AIC_IVR] str r14, [r14, #AIC_IVR] msr CPSR_c, #ARM_MODE_SVC

stmfd sp!, {r1-r3, r12, r14}

mov r14, pc

bx r0 ldmia sp!, {r1-r3, r12, r14}

msr CPSR_c, #ARM_MODE_IRQ | I_BIT

ldr r14, =AT91C_BASE_AIC

str r14, [r14, #AIC_EOICR] ldmia sp!, {r0,r14}

msr SPSR_cxsf, r14 ldmia sp!, {pc}^

.section .text

reset_handler: ldr pc, =_low_level_init _low_level_init:

ldr r2, =_lp_ll_init ldmia r2, {r0, r1} mov sp, r1 mov lr, pc bx r0 _remap:

ldr r2, _lp_remap mov r0, #AT91C_MC_RCB str r0, [r2] _stack_init:

ldr r2, =_lp_stack_init ldmia r2, {r0, r1, r2} msr CPSR_c, #ARM_MODE_ABT | I_BIT | F_BIT

mov sp, r0 sub r0, r0, r1 msr CPSR_c, #ARM_MODE_IRQ | I_BIT | F_BIT

mov sp, r0 sub r0, r0, r2 msr CPSR_c, #ARM_MODE_SVC | F_BIT

mov sp, r0 _init_data:

ldr r2, =_lp_data ldmia r2, {r1, r3, r4} 1: cmp r3, r4 ldrcc r2, [r1], #4 strcc r2, [r3], #4 bcc 1b _init_bss:

ldr r2, =_lp_bss ldmia r2, {r3, r4} mov r2, #0 1: cmp r3, r4 strcc r2, [r3], #4 bcc 1b _branch_main:

ldr r0, =main mov lr, pc bx r0 _lp_ll_init:

.word lowlevel_init .word TOP_OF_MEMORY /* Default SVC stack after power up */ _lp_remap: .word AT91C_MC_RCR _lp_stack_init: .word TOP_OF_MEMORY /* Top of the stack */ .word ABT_STACK_SIZE /* ABT stack size */ .word IRQ_STACK_SIZE /* IRQ stack size */ _lp_bss: .word _sbss .word _ebss _lp_data: .word _etext .word _sdata .word _edata |

---------------------------------------------------------------------------------------------------------------------------

cstartup.S

cstartup.S